// PARTENAIRES

Contributions

// PARTENAIRES

Contributions

Émulateur générique et polyvalent

- Capable de générer des attaques sur un grand nombre d’IOs

- Accessible aux industriels, faible cout et facile d’utilisation

- Capable de tester un processeur multi-coeurs

Simulateur et algorithmes IA

- Apprentissage basé sur des données physiques

- Optimisation des simulateurs

- Prédiction de scenario d’attaques

Cœur durci et performant face aux cyberattaques

- Fautes simples et multiples Root-of-trust cœur RISC-V instancié sur FPGA

- Approches novatrices (statiques et dynamiques) pour vérifier la sécurité du cœur

Émulateur générique et polyvalent

- Capable de générer des attaques sur un grand nombre d’IOs

- Accessible aux industriels, faible cout et facile d’utilisation

- Capable de tester un processeur multi-coeurs

Simulateur et algorithmes IA

- Apprentissage basé sur des données physiques

- Optimisation des simulateurs

- Prédiction de scenario d’attaques

Cœur durci et performant face aux cyberattaques

- Fautes simples et multiples Root-of-trust cœur RISC-V instancié sur FPGA

- Approches novatrices (statiques et dynamiques) pour vérifier la sécurité du cœur

// PARTENAIRES

OVERVIEW

// PARTENAIRES

OVERVIEW

// PARTENAIRES

COMPETENCE PARTENAIRES

- Injection fautes sur plateformes FPGA

- Bancs de test cartes et FPGA

- Simulation impact des rayonnements ionisants

- Sureté fonctionnelle circuits ASIC

- Architecture des systèmes embarqués

- Fiabilité, sureté, sécurité

- Injection fautes sur plateformes FPGA

- Bancs de test cartes et FPGA

- Simulation impact des rayonnements ionisants

- Sureté fonctionnelle circuits ASIC

- Architecture des systèmes embarqués

- Fiabilité, sureté, sécurité

// PARTENAIRES

RETOMBÉES

// Publications - Dissémination - Brevets

RETOMBEES SCIENTIFIQUES

RETOMBEES SCIENTIFIQUES

ET TECHNIQUES

- Techniques d’émulation sur la vulnérabilité des composants

- Gestion temps réel d’un grand nombre de signaux à fréquence élevée

- Développement IPs génération de fautes, cohérence des domaines d’horloge etc.

- Méthodes d’apprentissage par IA appliquées aux attaques

- Apporter des nouveaux concepts sur la sécurité des micro-architectures aux attaques physiques

// Publications - Dissémination - Brevets

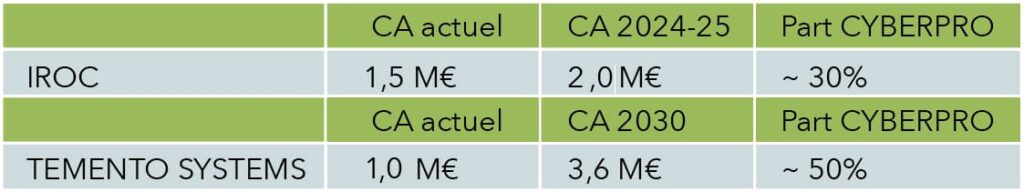

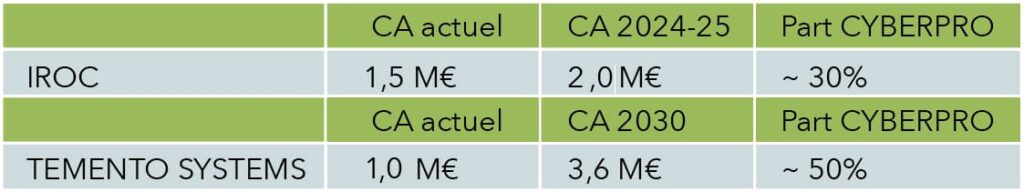

RETOMBEES INDUSTRIELLES ET ECONOMIQUES

- Valorisation économique, retombées et filières

Objectif: Contribuer à développer une filière économique et industrielle dans le domaine de la cybersécurité des processeurs embarqués. - Apporter des services et des outils pour tester et évaluer le niveau de vulnérabilité des processeurs

- Moyens de certification et de validation

26 emplois créés à l'horizon 2030

// Publications - Dissémination - Brevets

RETOMBEES SCIENTIFIQUES

RETOMBEES SCIENTIFIQUES

ET TECHNIQUES

- Techniques d’émulation sur la vulnérabilité des composants

- Gestion temps réel d’un grand nombre de signaux à fréquence élevée

- Développement IPs génération de fautes, cohérence des domaines d’horloge etc.

- Méthodes d’apprentissage par IA appliquées aux attaques

- Apporter des nouveaux concepts sur la sécurité des micro-architectures aux attaques physiques

// Publications - Dissémination - Brevets

RETOMBEES INDUSTRIELLES ET ECONOMIQUES

- Valorisation économique, retombées et filières

Objectif: Contribuer à développer une filière économique et industrielle dans le domaine de la cybersécurité des processeurs embarqués. - Apporter des services et des outils pour tester et évaluer le niveau de vulnérabilité des processeurs

- Moyens de certification et de validation

26 emplois créés à l'horizon 2030

// PARTENAIRES

SYNOPTIQUE

SYNOPTIQUE

PROJET

// PARTENAIRES

SYNOPTIQUE PROJET

(*) 30 à 40% des personnes interrogées déclarent que la sécurité est le principal obstacle à surmonter dans les systèmes embarqués.

(*) Eseye the future of IoT report 2002